//-----------------------------------------------------------------------------------

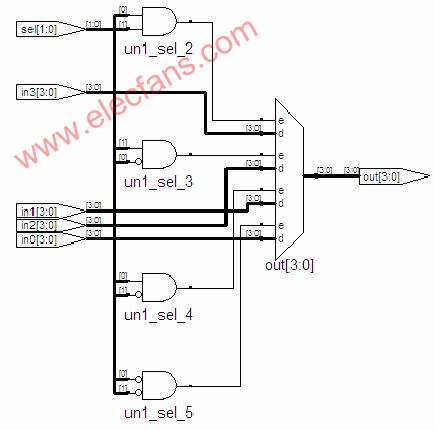

// DESCRIPTION?? :? Multiplexer

//??????????? Code style: used case statement

//????????????????? Width of output terminal: 8

//????????????????? Number of terminals: 4

//????????????????? Output enable active: HIGH

//????????????????? Output value of all bits when enable not active: 0

//-----------------------------------------------------------------------------------

module mux(EN ,IN0 ,IN1 ,IN2 ,IN3 ,SEL ,OUT );

input? EN ;

input? [7:0] IN0 ,IN1 ,IN2 ,IN3 ;

input? [1:0] SEL ;

output [7:0] OUT ;

reg? [7:0] OUT ;

always @(SEL? or EN? or IN0? or IN1? or IN2? or IN3 )

begin

if (EN? == 0) OUT? = {8{1'b0}};

else

case (SEL )

0 : OUT? = IN0 ;

1 : OUT? = IN1 ;

2 : OUT? = IN2 ;

3 : OUT? = IN3 ;

default : OUT? = {8{1'b0}};

endcase

end

endmodule

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論